Inline Group CTC

КТЦ ИНЛАЙН ГРУПП

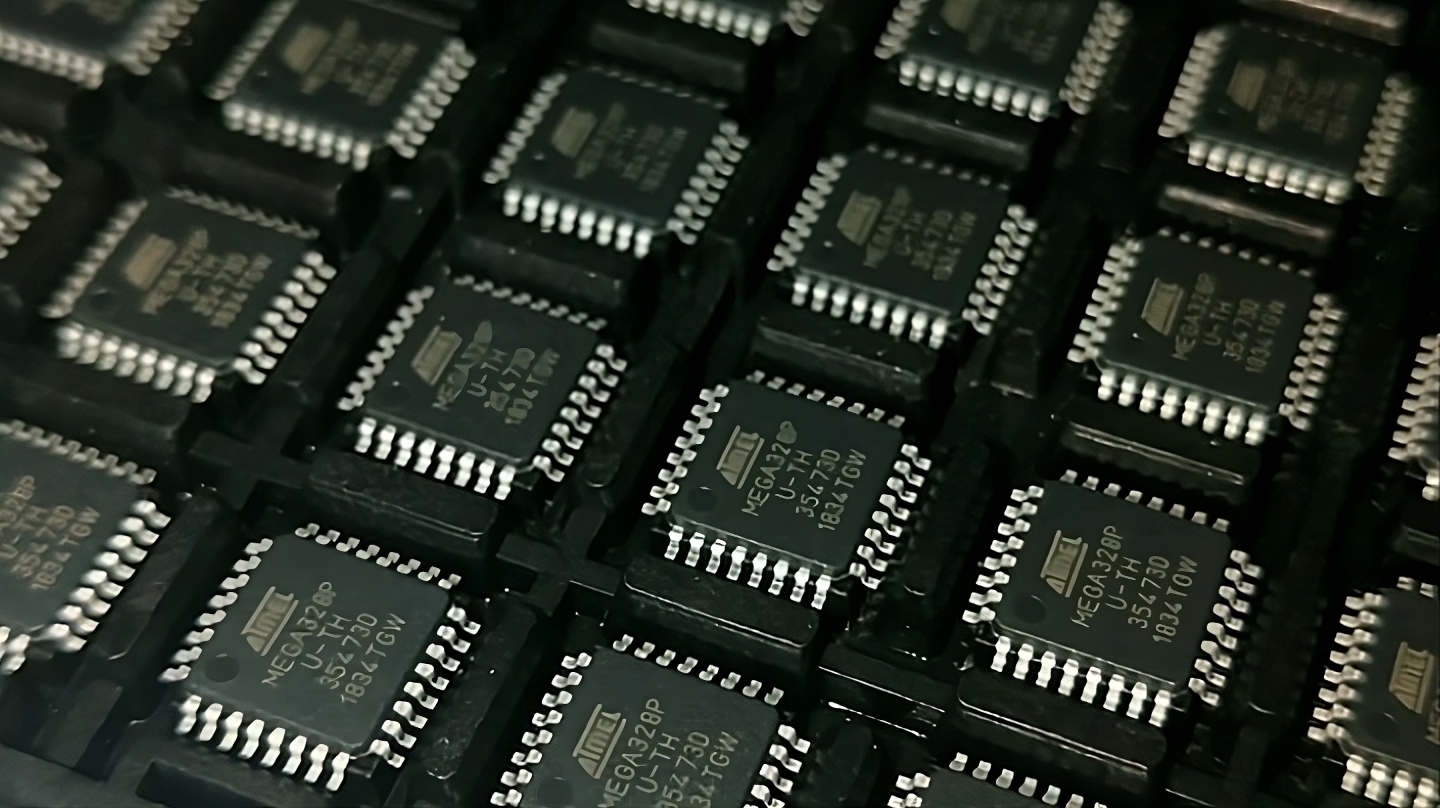

Ведущий поставщик электронных компонентов на территории РФ

о нас

Почему нас выбирают

| В основе нашей работы лежит индивидуальный подход к клиенту, благодаря этому мы работаем с передовыми компаниями различных отраслей российской экономики. Inline Group CTC поддерживает партнерские отношения с лучшими поставщиками Китая и других стран Юго-Восточной Азии. На всех этапах проектирования и производства мы предоставляем нашим Заказчикам квалифицированную поддержку опытных технических специалистов. |

о нас

Наши преимущества

- Официальный дистрибьютер компаний Xilinx, SoCе, RELEUM до 2022 г.

- Более 20 лет на рынке РФ

- Обучение по продуктам AMD (Xilinx), Intel FPGA (Altera), Siemens (Mentor Graphics)

20 лет работы на рынке

Индивидуальный подход к каждому клиенту

Гибкая ценовая политика

Быстрые сроки поставки

Проверенные поставщики

Технических поддержка

Мы предлагаем:

- Поставку электронных компонентов

- Инженерную поддержку проектов

- Обучение

УСЛУГИ

КТЦ Инлайн Групп поставляет электронные компоненты отечественного и иностранного производства.

Для заказа заполните Форму обратной связи внизу страницы и мы с вами свяжемся!

Для заказа заполните Форму обратной связи внизу страницы и мы с вами свяжемся!

товары

Каталог

В НАЛИЧИИ НА СКЛАДЕ

Складские позиции из наличия высылаются клиенту по запросу

Складские позиции из наличия высылаются клиенту по запросу

ПОД ЗАКАЗ ПО ЗАПРОСУ

Свяжитесь с нами для заказа через форму внизу сайта

Свяжитесь с нами для заказа через форму внизу сайта

Контакты

Напишите нам!